応用情報技術者 2011年 春期 午前2 問24

問題文

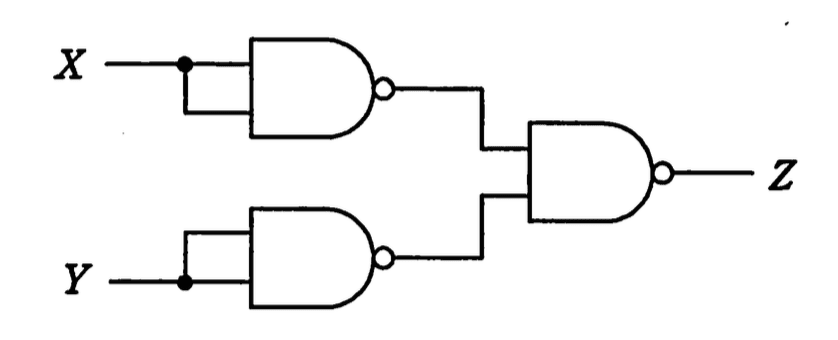

NAND 素子を用いた次の組合せ回路の出力を表す式はどれか。ここで、論理式中の・は論理積、+は論理和、はXの否定を表す。

選択肢

ア:

イ:(正解)

ウ:

エ:

NAND素子を用いた組合せ回路の出力式【午前2 解説】

要点まとめ

- 結論:この回路の出力は論理和 に等しいです。

- 根拠:NANDゲート3つの組み合わせでOR回路を構成しているため、出力は となります。

- 差がつくポイント:NANDゲートの否定特性を利用し、De Morganの法則を正しく適用できるかが鍵です。

正解の理由

この回路は、2入力NANDゲートを2つ使い、それぞれの入力にXとYを分岐して接続しています。各NANDゲートの出力は と のように見えますが、実際はXとYが別々のNANDゲートに入力されているため、出力は ではなく、単に ではありません。

次に、これら2つのNANDゲートの出力を3つ目のNANDゲートの入力に並列接続しています。3つ目のNANDゲートはこれらの出力の論理積の否定を返します。

この構成は、De Morganの法則により、 となり、選択肢の中で唯一該当するのはイ: です。

次に、これら2つのNANDゲートの出力を3つ目のNANDゲートの入力に並列接続しています。3つ目のNANDゲートはこれらの出力の論理積の否定を返します。

この構成は、De Morganの法則により、 となり、選択肢の中で唯一該当するのはイ: です。

よくある誤解

NANDゲートは否定論理積と覚えがちですが、複数のNANDゲートを組み合わせるとANDやORなど他の基本論理回路を構成できる点を見落としやすいです。

解法ステップ

- 入力XとYがそれぞれ2本に分岐し、2つのNANDゲートに入力されていることを確認する。

- それぞれのNANDゲートの出力は ではなく、ではないことに注意。

- 2つのNANDゲートの出力を3つ目のNANDゲートに入力し、その出力を考える。

- De Morganの法則を用いて、 と導く。

- 選択肢の中から を選ぶ。

選択肢別の誤答解説

- ア:

NANDゲートはANDの否定なので、単純にANDとはならず誤りです。 - イ:

正解。NANDゲート3つの組み合わせでOR回路を実現しています。 - ウ:

入力の否定が片方だけであり、回路構成と合いません。 - エ:

ORの否定はNANDゲート1つで表せますが、この回路は3つのNANDゲートでORを実現しているため誤りです。

補足コラム

NANDゲートは「万能ゲート」と呼ばれ、これ1種類だけでAND、OR、NOTなど全ての基本論理回路を構成可能です。特に、2入力NANDゲート3つでOR回路を作る方法は基本的な回路設計の知識として重要です。

FAQ

Q: なぜNANDゲートだけでOR回路が作れるのですか?

A: De Morganの法則により、 と表せるため、NANDゲートの否定論理積を組み合わせてOR回路を実現できます。

A: De Morganの法則により、 と表せるため、NANDゲートの否定論理積を組み合わせてOR回路を実現できます。

Q: NANDゲートの出力に付いているバブルは何を意味しますか?

A: バブルは論理否定(NOT)を示し、NANDゲートの出力がANDの否定であることを表しています。

A: バブルは論理否定(NOT)を示し、NANDゲートの出力がANDの否定であることを表しています。

関連キーワード: NANDゲート、De Morganの法則、論理回路、組合せ回路、論理和、論理積、否定論理

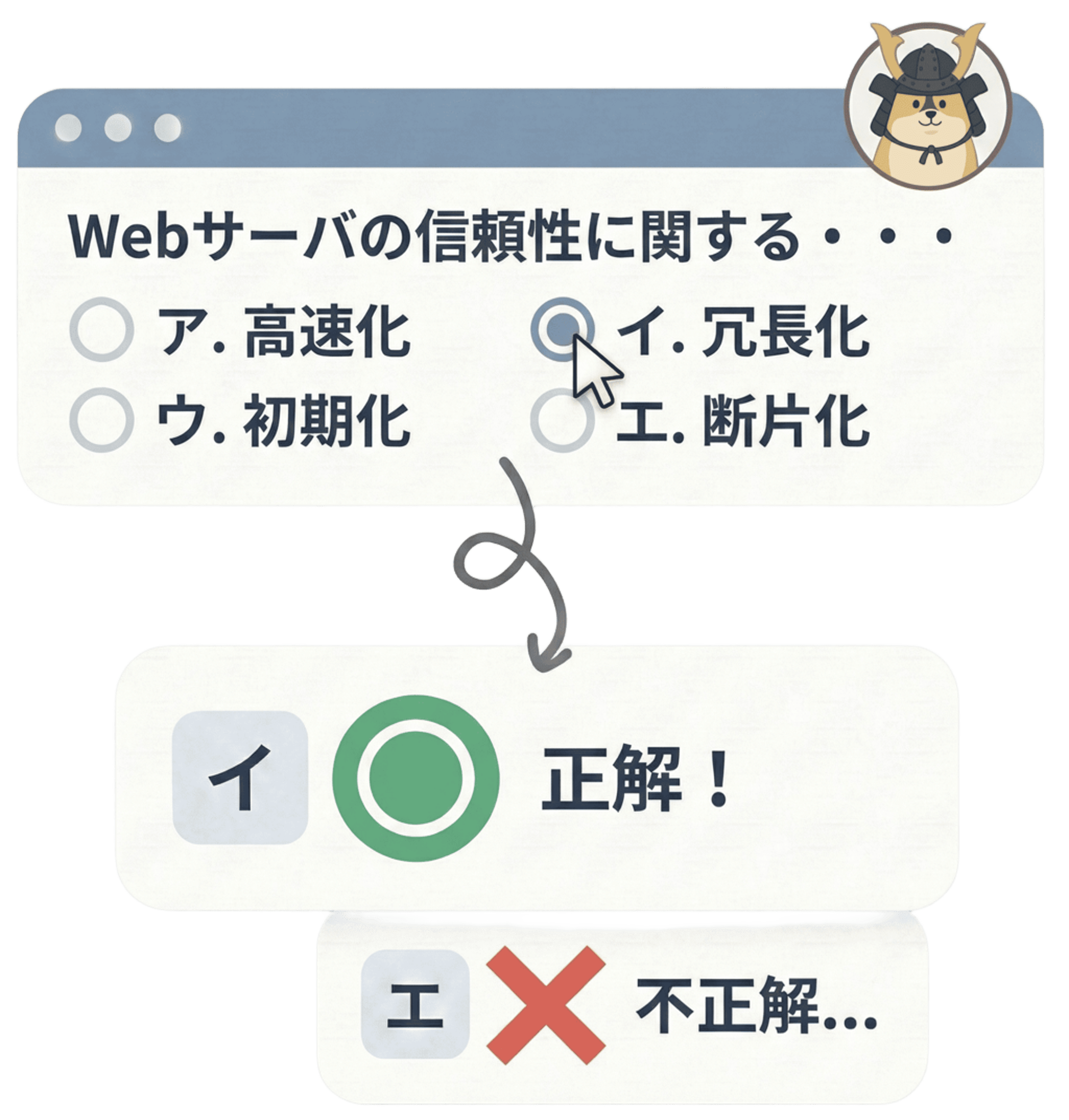

\ せっかくなら /

応用情報技術者を

クイズ形式で学習しませんか?

クイズ画面へ遷移する→

すぐに利用可能!