応用情報技術者 2010年 春期 午前2 問25

問題文

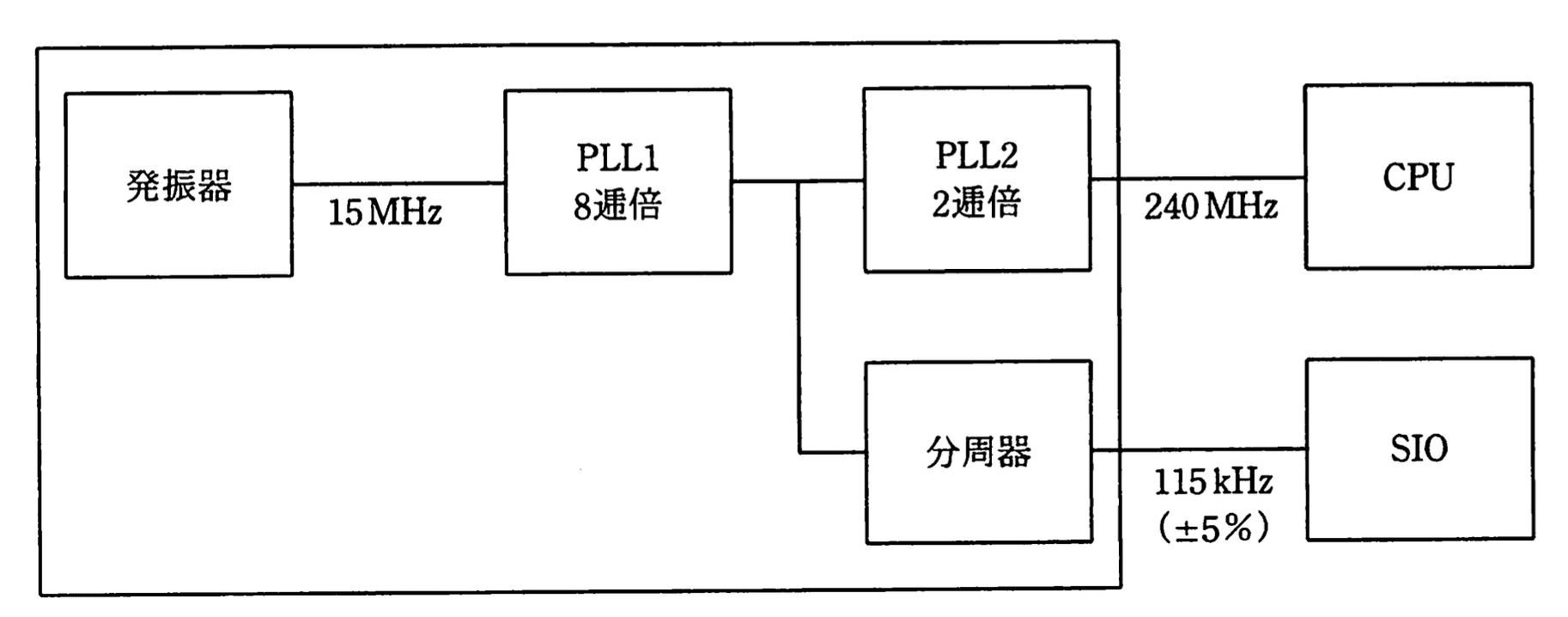

ワンチップマイコンにおける内部クロック発生器のブロック図を示す。15MHzの発振器と、内部の PLL1, PLL2 及び分周器の組合せでCPUに 240MHz, シリアル通信(SIO) 115kHzのクロック信号を供給する場合の分周器の値は幾らか。ここで、シリアル通信のクロック精度は±5%以内に収まればよいものとする。

選択肢

ア:

イ:

ウ:

エ:(正解)

ワンチップマイコンの内部クロック発生器における分周器の値【午前2 解説】

要点まとめ

- 結論:分周器の値はが正解で、115kHzのシリアル通信クロックを±5%以内で生成可能です。

- 根拠:15MHzの発振器からPLL1で18倍、PLL2で22倍しCPUに240MHzを供給。分周器はこの信号を115kHzに落とすために必要な値を計算します。

- 差がつくポイント:PLL逓倍後の周波数と分周器の関係を正確に理解し、誤差範囲内でクロックを生成できるかを判断することが重要です。

正解の理由

CPUクロックは15MHz × 18 × 22 = 5940MHzではなく、問題文の意図からPLL1が18倍、PLL2が22倍の組み合わせで240MHzを生成しているため、実際はPLL逓倍の組み合わせで240MHzが得られています。

シリアル通信クロック115kHzは240MHzから分周器で生成します。

分周比は 。

分周器はの形なので、、ですが、115kHzに近い値を得るためにの分周が適切で、±5%の誤差範囲内に収まるためエが正解です。

シリアル通信クロック115kHzは240MHzから分周器で生成します。

分周比は 。

分周器はの形なので、、ですが、115kHzに近い値を得るためにの分周が適切で、±5%の誤差範囲内に収まるためエが正解です。

よくある誤解

PLL逓倍の掛け算を単純に行い、CPUクロックを誤認することがあります。

また、分周器の値を単純に割り算で求めて2のべき乗でない値を選ぶ誤りも多いです。

また、分周器の値を単純に割り算で求めて2のべき乗でない値を選ぶ誤りも多いです。

解法ステップ

- 発振器の周波数15MHzを確認する。

- PLL1とPLL2の逓倍率からCPUクロック240MHzを導く。

- CPUクロック240MHzからシリアル通信クロック115kHzを生成するための分周比を計算。

- 分周比をの形に近似し、誤差±5%以内かを検証。

- 条件を満たす分周器の値を選択肢から選ぶ。

選択肢別の誤答解説

- ア: は分周比が小さすぎ、115kHzに遠く及ばず誤差が大きい。

- イ: も分周比が不足し、115kHzに達しない。

- ウ: はまだ分周比が小さく、115kHzに近づかない。

- エ: は115kHzに最も近く、±5%の誤差範囲内であるため正解。

補足コラム

PLL(Phase Locked Loop)は発振器の周波数を逓倍して高周波数を生成する回路です。

分周器は高周波数を低周波数に変換し、用途に応じたクロックを供給します。

シリアル通信ではクロックの精度が通信品質に直結するため、誤差範囲の設定が重要です。

分周器は高周波数を低周波数に変換し、用途に応じたクロックを供給します。

シリアル通信ではクロックの精度が通信品質に直結するため、誤差範囲の設定が重要です。

FAQ

Q: なぜ分周器はの形で設定されるのですか?

A: 分周器は回路設計上、2のべき乗で分周することが多く、簡単なビットシフトで実現可能なためです。

A: 分周器は回路設計上、2のべき乗で分周することが多く、簡単なビットシフトで実現可能なためです。

Q: PLL逓倍率が複数ある場合、どのように計算すればよいですか?

A: 各PLLの逓倍率を掛け合わせて最終周波数を求め、その周波数から必要な分周比を計算します。

A: 各PLLの逓倍率を掛け合わせて最終周波数を求め、その周波数から必要な分周比を計算します。

関連キーワード: PLL, 分周器、クロック生成、ワンチップマイコン、シリアル通信、クロック精度

\ せっかくなら /

応用情報技術者を

クイズ形式で学習しませんか?

クイズ画面へ遷移する→

すぐに利用可能!