応用情報技術者 2023年 秋期 午前2 問22

問題文

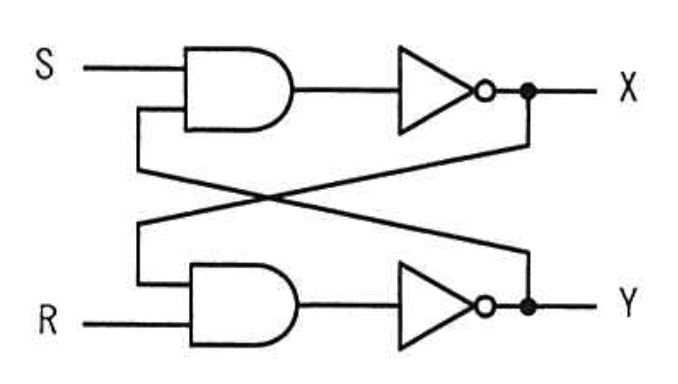

図の論理回路において、S=1, R=1, X=0, Y=1のとき、Sを一旦0にした後、再びに戻した。この操作を行った後のX, Yの値はどれか。

選択肢

ア:X=0, Y=0

イ:X=0, Y=1

ウ:X=1, Y=0(正解)

エ:X=1, Y=1

フィードバック回路の動作解析【午前2 解説】

要点まとめ

- 結論:S=1, R=1, X=0, Y=1の状態からSを0にし再び1に戻すと、X=1、Y=0となる。

- 根拠:この回路はSRラッチ(NANDゲート版)で、S=R=1は保持状態、S=0でセット動作、S=1に戻すと状態が固定される。

- 差がつくポイント:フィードバック回路の動作理解と、NANDゲートSRラッチの入力条件による出力変化を正確に把握できるかが鍵。

正解の理由

この回路はNANDゲート2つとインバータ2つで構成されたSRラッチです。

初期状態はS=1, R=1でX=0, Y=1。ここでSを0にすると、上部NANDゲートの出力が強制的に1となり、Xの値が変化します。

その後Sを1に戻すと、ラッチはセット状態を保持し、X=1、Y=0となります。

したがって、正解はウ: X=1, Y=0です。

初期状態はS=1, R=1でX=0, Y=1。ここでSを0にすると、上部NANDゲートの出力が強制的に1となり、Xの値が変化します。

その後Sを1に戻すと、ラッチはセット状態を保持し、X=1、Y=0となります。

したがって、正解はウ: X=1, Y=0です。

よくある誤解

- S=R=1の状態は「リセット」や「セット」ではなく「保持」状態であると誤解しやすい。

- フィードバック回路の信号の流れを逆に考えてしまうことが多い。

解法ステップ

- 初期状態の入力と出力を確認(S=1, R=1, X=0, Y=1)。

- Sを0にしたときの上部NANDゲートの出力を計算。

- 出力変化がX、Yにどう影響するかを追う。

- Sを1に戻した後の状態を再度計算し、安定状態を判断。

- 最終的なX、Yの値を選択肢と照合。

選択肢別の誤答解説

- ア: X=0, Y=0

→ 両方0はNANDラッチの動作として不安定であり、今回の操作ではありえない。 - イ: X=0, Y=1

→ 初期状態のままで変化がないと誤解した場合の選択。Sを0にした影響を無視している。 - ウ: X=1, Y=0

→ 正解。Sを0にしてセット動作を行い、Sを1に戻した後の保持状態。 - エ: X=1, Y=1

→ NANDラッチの特性上、XとYが同時に1になることはない。

補足コラム

SRラッチは基本的なメモリ素子で、NANDゲート版は入力が両方1のときに状態を保持します。

SやRが0になると、それぞれセットやリセット動作を行い、出力が変化します。

この動作を理解することは、フリップフロップなどのより複雑な回路設計の基礎となります。

SやRが0になると、それぞれセットやリセット動作を行い、出力が変化します。

この動作を理解することは、フリップフロップなどのより複雑な回路設計の基礎となります。

FAQ

Q: なぜS=R=1が保持状態なのですか?

A: NANDゲートSRラッチでは、両方の入力が1のとき出力は前の状態を維持するため、状態が変わりません。

A: NANDゲートSRラッチでは、両方の入力が1のとき出力は前の状態を維持するため、状態が変わりません。

Q: Sを0にすると何が起こりますか?

A: Sが0になると、上部NANDゲートの出力が強制的に1となり、セット動作が起こりXが1に変わります。

A: Sが0になると、上部NANDゲートの出力が強制的に1となり、セット動作が起こりXが1に変わります。

関連キーワード: SRラッチ、NANDゲート、フィードバック回路、論理回路、メモリ素子、ラッチ回路

\ せっかくなら /

応用情報技術者を

クイズ形式で学習しませんか?

クイズ画面へ遷移する→

すぐに利用可能!