応用情報技術者 2018年 春期 午前2 問22

問題文

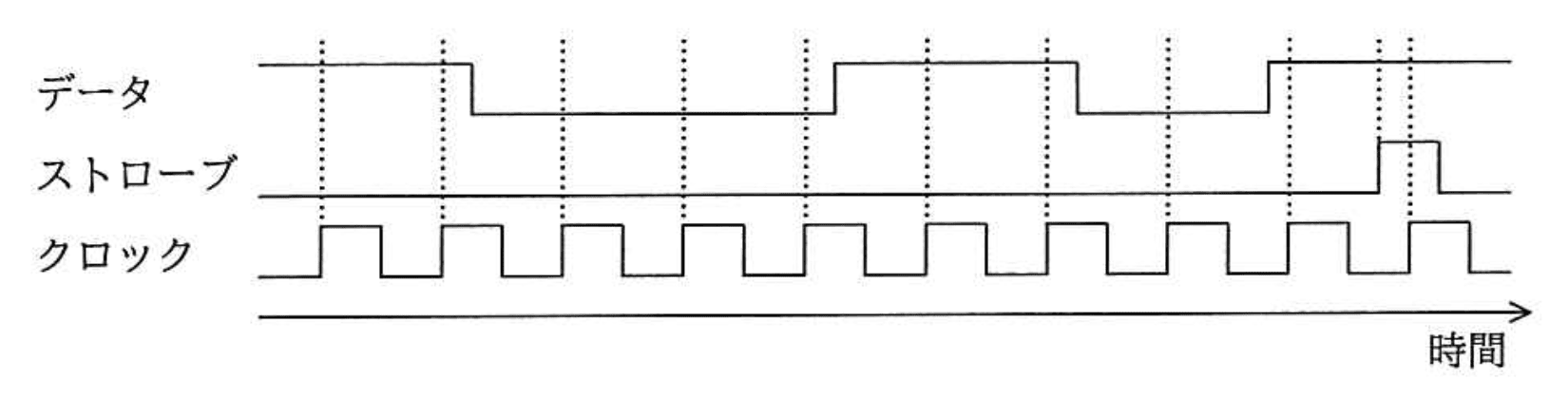

クロックの立上りエッジで、データを入力の最下位ビットに取り込んで上位方向へシフトし、ストローブの立上りエッジで値を確定する 8ビットのシリアル入力パラレル出力シフトレジスタがある。各信号の波形を観測した結果が図のとおりであるとき、確定後のシフトレジスタの値はどれか。ここで、数値は16進数で表記している。

選択肢

ア:63

イ:8D(正解)

ウ:B1

エ:C6

シリアル入力パラレル出力シフトレジスタの動作解析【午前2 解説】

要点まとめ

- 結論:クロックの立上りエッジでデータをLSBに取り込み、ストローブの立上りで値を確定するため、最終的なレジスタ値は「8D」となる。

- 根拠:クロック立上り8回分のデータ取り込みを時系列で追い、ストローブ立上り直前のシフトレジスタの状態を確認した。

- 差がつくポイント:クロックとストローブのタイミング関係を正確に把握し、データの取り込み順序(LSBから上位へシフト)を理解することが重要。

正解の理由

選択肢イ「8D」は、クロックの立上り8回にわたりデータ波形の値をLSBから順に取り込み、ストローブの立上りエッジで値を確定した結果と一致します。具体的には、データのHigh/Lowの変化をクロック立上りで読み取り、8ビット分シフトして格納。ストローブが立ち上がる第8点線直後の状態が「8D(16進数)」となるため正解です。

よくある誤解

クロックとストローブのタイミングを混同し、ストローブ立上り前の値を確定値と誤認することがあります。また、データの取り込み方向(LSBから上位へ)を逆に考えるミスも多いです。

解法ステップ

- クロックの立上りエッジを8回数える(第1~第8点線間)。

- 各クロック立上りでデータ波形の状態をLSBに取り込む。

- 取り込んだビットを上位方向へシフトしながら8ビット分蓄積。

- ストローブの立上りエッジ(第8点線直後)でシフトレジスタの値を確定。

- 確定時の8ビット値を16進数に変換し、選択肢と照合。

選択肢別の誤答解説

- ア「63」:データ取り込み順序やクロック回数が不足しており、正しいシフト結果と合致しません。

- イ「8D」:正解。クロック8回分のデータ取り込みとストローブのタイミングに合致。

- ウ「B1」:データ波形のHigh/Lowのタイミングを誤認し、誤ったビット列を形成しています。

- エ「C6」:シフト方向やデータ取り込みタイミングの理解不足により誤った値となっています。

補足コラム

シリアル入力パラレル出力(SIPO)シフトレジスタは、クロックの立上りで1ビットずつデータを取り込み、内部でシフトしながら蓄積します。ストローブ信号は、内部レジスタの値を外部に確定・出力するタイミング制御に使われます。クロックとストローブの同期関係を正確に理解することが、設問の正答に不可欠です。

FAQ

Q: なぜデータはLSBから取り込むのですか?

A: 問題文に「データを入力の最下位ビットに取り込む」と明記されており、シフトレジスタの基本動作としてLSBから順にシフトアップします。

A: 問題文に「データを入力の最下位ビットに取り込む」と明記されており、シフトレジスタの基本動作としてLSBから順にシフトアップします。

Q: ストローブ信号は何のために使うのですか?

A: ストローブの立上りエッジでシフトレジスタの値を確定し、外部に出力するタイミングを制御します。

A: ストローブの立上りエッジでシフトレジスタの値を確定し、外部に出力するタイミングを制御します。

Q: クロックの立上りエッジ以外でデータは取り込まれますか?

A: いいえ。問題文の条件から、データはクロックの立上りエッジでのみ取り込まれます。

A: いいえ。問題文の条件から、データはクロックの立上りエッジでのみ取り込まれます。

関連キーワード: シフトレジスタ、シリアル入力パラレル出力、クロック同期、ストローブ信号、ビットシフト、16進数表記

\ せっかくなら /

応用情報技術者を

クイズ形式で学習しませんか?

クイズ画面へ遷移する→

すぐに利用可能!