応用情報技術者 2019年 春期 午前2 問23

問題文

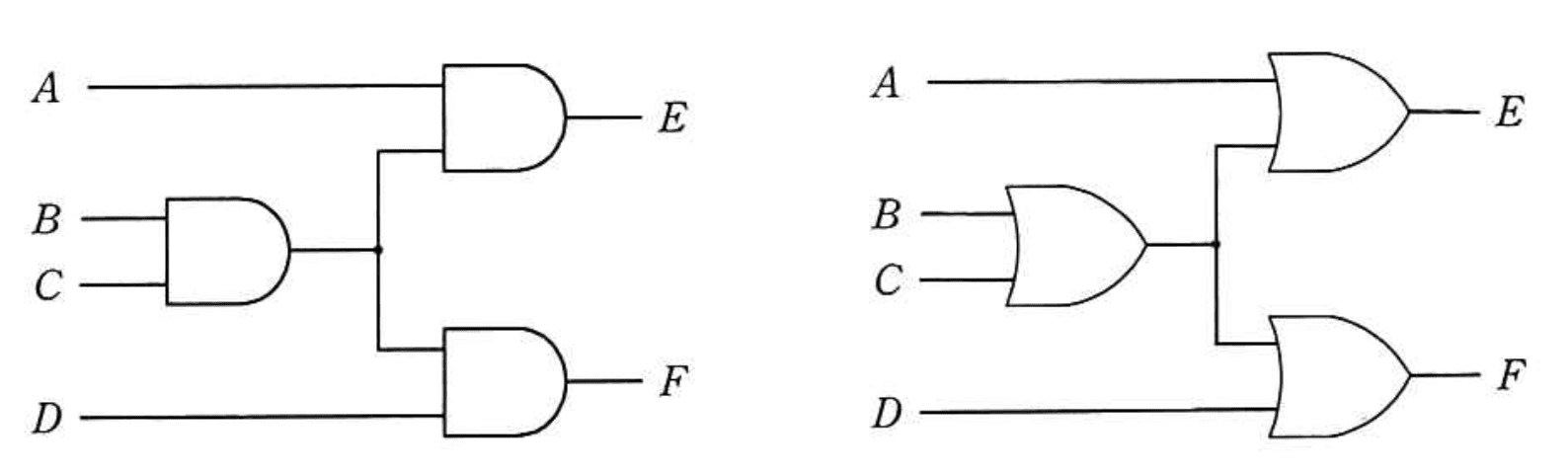

次の二つの回路の入力に値を与えたとき、表の入力A, B, C, Dと出力E, Fの組合せのうち、全ての素子が論理積素子で構成された左側の回路でだけ成立するものはどれか。

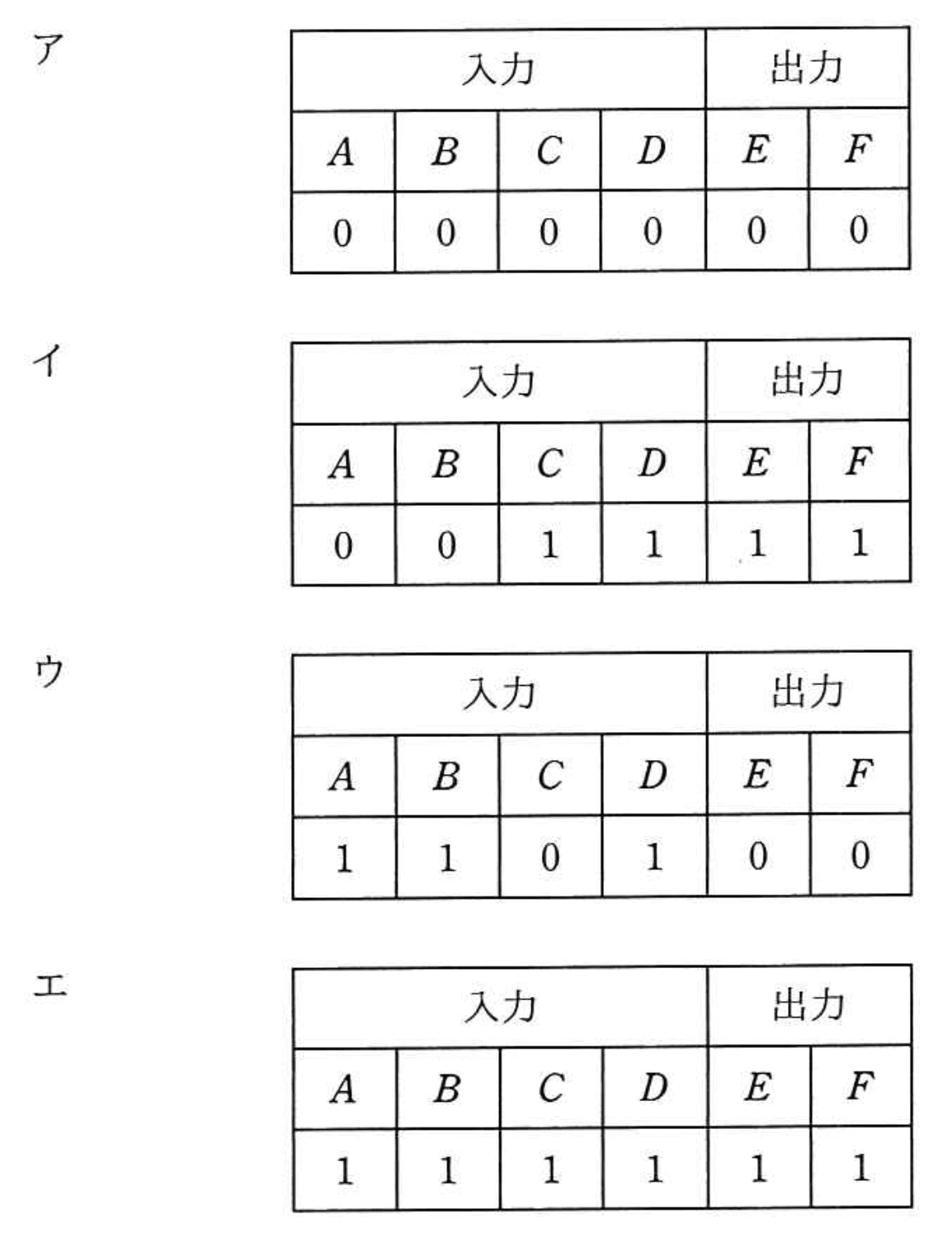

選択肢

ア:

イ:

ウ:(正解)

エ:

論理積素子のみで構成された回路の出力判定【午前2 解説】

要点まとめ

- 結論:左側回路は全てANDゲートで構成されており、出力は入力の論理積で決まるため、選択肢ウのみ成立します。

- 根拠:左回路のEはAと(B AND C)のAND、FはDと(B AND C)のANDであり、全てAND演算であることがポイントです。

- 差がつくポイント:ANDとORの違いを正確に理解し、入力と出力の論理式を丁寧に書き出して検証することが重要です。

正解の理由

左側回路はすべて論理積(AND)素子で構成されているため、出力EとFは以下のように表せます。

- 中央のANDゲートの出力:

- 出力E:

- 出力F:

選択肢ウの入力は であり、

よって、出力E=0、F=0となり、選択肢ウの出力と一致します。

他の選択肢はAND回路の論理式に合致しません。

他の選択肢はAND回路の論理式に合致しません。

よくある誤解

AND回路の出力をOR回路のように考え、入力のどれかが1なら出力も1になると誤解しやすいです。

また、分岐点からの信号が単純にコピーされると誤認することもあります。

また、分岐点からの信号が単純にコピーされると誤認することもあります。

解法ステップ

- 左側回路の論理構成を確認し、全てANDゲートであることを把握する。

- 中央のANDゲートの出力をと表す。

- 出力Eは、出力Fはと論理式を立てる。

- 各選択肢の入力値を代入し、EとFの値を計算する。

- 計算結果と選択肢の出力が一致するものを選ぶ。

選択肢別の誤答解説

- ア:全て0の入力で、、は正しいが、入力A=0,D=0のためE,F=0は当然であり、左回路だけの成立条件ではない。

- イ:で、E,Fは0のはずが1となっており左回路では成立しない。

- ウ:で、E,F=0となり左回路の論理式に合致。

- エ:全て1で、E,F=1となり左回路でも成立しそうだが、右回路でも成立するため「左回路でだけ成立」ではない。

補足コラム

論理積(AND)ゲートは全ての入力が1のときのみ出力が1になる基本素子です。

分岐点からの信号は単なる配線であり、論理演算は行いません。

論理和(OR)ゲートとの違いを理解することはデジタル回路設計の基礎です。

分岐点からの信号は単なる配線であり、論理演算は行いません。

論理和(OR)ゲートとの違いを理解することはデジタル回路設計の基礎です。

FAQ

Q: なぜ分岐点からの信号はそのままコピーされるのですか?

A: 分岐点は単なる配線の分岐であり、信号の論理値を変えずに複数の入力へ送る役割を持ちます。

A: 分岐点は単なる配線の分岐であり、信号の論理値を変えずに複数の入力へ送る役割を持ちます。

Q: AND回路で出力が1になる条件は?

A: 全ての入力が1のときのみ出力が1になります。

A: 全ての入力が1のときのみ出力が1になります。

関連キーワード: 論理積、ANDゲート、デジタル回路、論理回路、入力出力解析

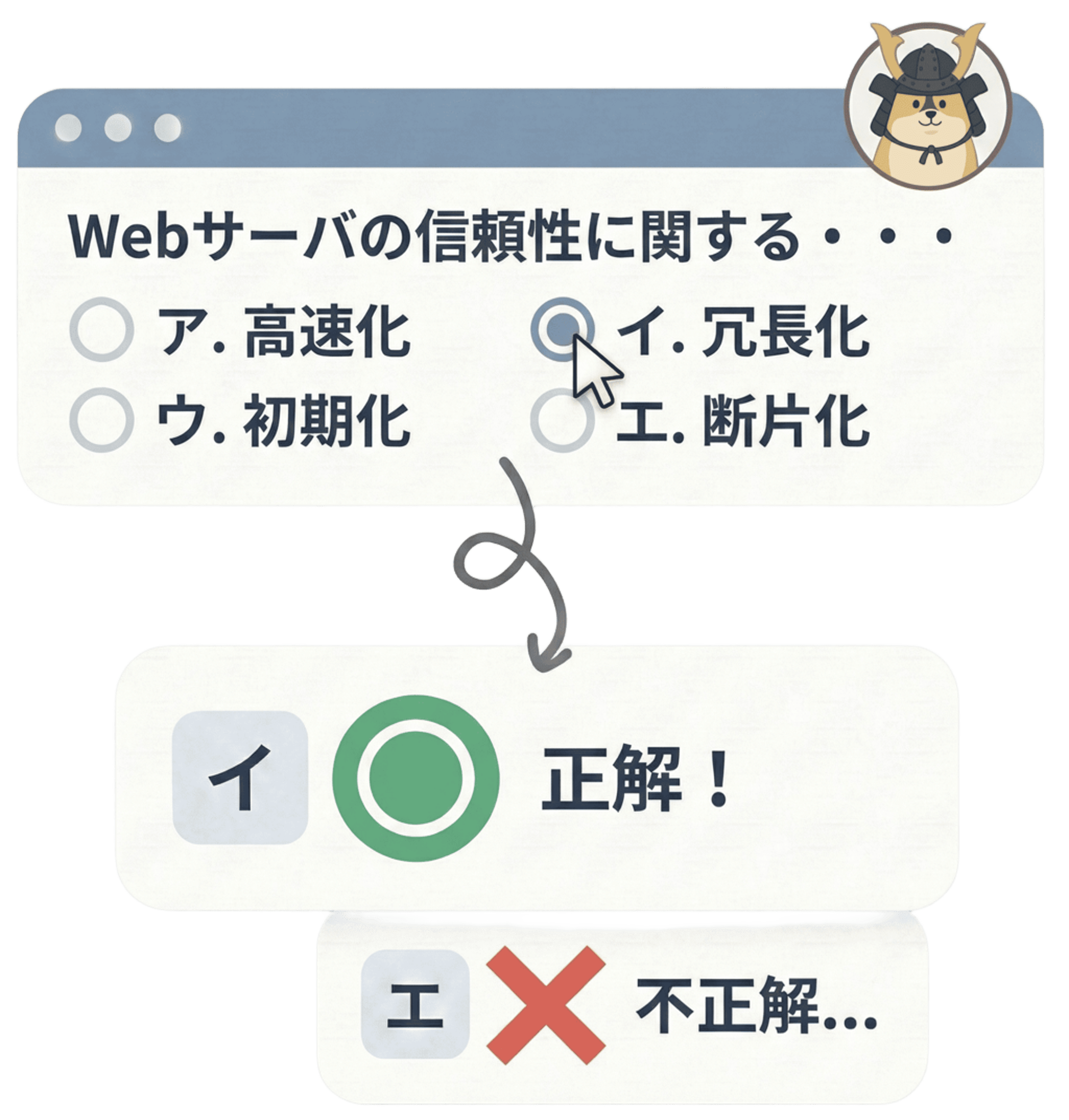

\ せっかくなら /

応用情報技術者を

クイズ形式で学習しませんか?

クイズ画面へ遷移する→

すぐに利用可能!